MMCへのeMEGAsimの実際の応用事例

パワーエレクトロニクス

MMCへのeMEGAsimの実際の応用事例

Modular Multilevel Converters(以下、MMC)は使用するスイッチ数が非常に多い為、効率的な 制御システムの開発が課題となっております。特に試作機で種々の制御方式を比較検討する場合など、実機用に使われているコントローラベースで制御システムを 開発するのは膨大な労力と時間が必要になります。

現在市場にあるラピッドプロトタイピング用リアルタイムシミュレーションシステムでは、MMCで要求される

20μsec程度の制御ステップに対応できず、これまでMMCのリアルタイムシミュレーションは、非常に難しいと

されてきました。

実際に数百から千個以上もあるスイッチを正確に時間遅れが無く模擬することは はほとんど不可能とさえ言われてきております。

OPAL-RTはこの問題を、eMEGAsimリアルタイムシミュレータ上で独自のアルゴリズムとFPGAの採用により 解決し、全体を20μsec以下の制御(積分刻み)ステップで正確に動作させることに世界で初めて成功しました。

実際に数百から千個以上もあるスイッチを正確に時間遅れが無く模擬することは はほとんど不可能とさえ言われてきております。

OPAL-RTはこの問題を、eMEGAsimリアルタイムシミュレータ上で独自のアルゴリズムとFPGAの採用により 解決し、全体を20μsec以下の制御(積分刻み)ステップで正確に動作させることに世界で初めて成功しました。

MMCの回路

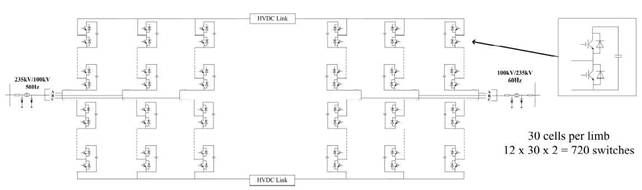

2つの交流系統を連系するMMC HVDCのリアルタイムシミュレーションです。変換器は各相60セルで、 各セルは2個のスイッチング素子(逆並列ダイオード付き)と1個のキャパシタからなるハーフブリッジです。

Fig. 1 Modular Multi-level Converter(MMC)の構成

実際には左右交流系統が接続されています。

変換器は途中が省略されていますが、各アームに30個のセルが直列に接続されています。

各々のセルはIGBTが2個直列につながり、それぞれに逆並列ダイオードが接続され、キャパシタが 並列におかれた単相インバータです。

スイッチング素子の数は、左右に12本のアーム、それぞれが30セル、 各セルにスイッチが2個で、合計12×30×2=720個となります。

OPAL-RTのリアルタイムシミュレータの制御(積分)時間周期は20μsです。

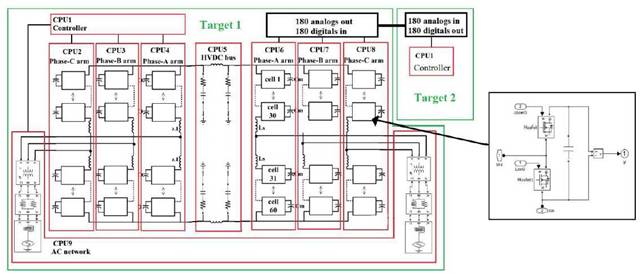

Fig.2 リアルタイムシミュレータの構成とHILS試験のためのモデルの分散配置

Fig2はモデルを2台のeMEGAsim HILS(Target1,Target2)にどのように配分しているかを示したものです。

各々のHILSには4コア×2=8コア(CPUコア)が配置されています。

(現在は6×2=12コアが主流です)

変換器モデルと制御回路モデルは、それぞれ別々のHILSハードウエアにダウンロードされ、IO端子を介して ケーブルで接続されています。

制御回路用HILSの出力信号で変換器用HILS内スイッチング素子が点弧され、 変換器側のキャパシタ電圧がI/O系由で制御回路用のHILSに送られます。

Target1にはMMCの主回路とAC/DC変換器のコントローラが置かれています。

Target2にはDC/AC変換器のコントローラが置かれています。

Target1とTarget2の間で、180のディジタル信号(各セルの点弧信号)と 180のアナログ信号(各セルのキャパシタ電圧)の受け渡しが行なわれます。

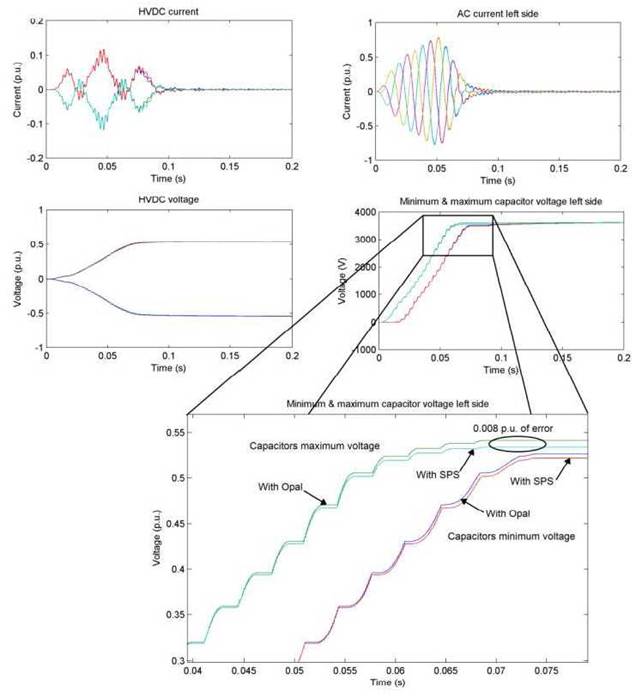

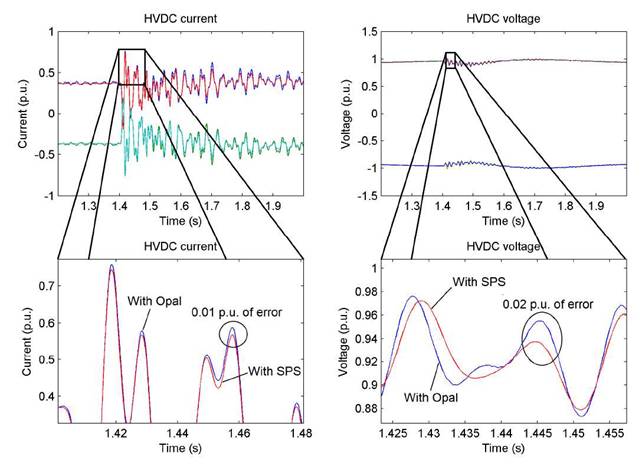

Fig3 自然整流モード - Simscape Electrical™(旧SimPowerSystems™)とOPAL-RT モデルの結果(制御ステップ20μs)

Fig.3は自然整流モードのシミュレーション結果です。

SimPowerSystemを使用し積分刻みを1μsecで オフラインで計算した結果をレファレンスとして、HILSシミュレーションの結果を比較しました。

SimPowerSystemのモデルは基本的に可変ステップで動作する為、固定ステップのHILSで使用する場合には 注意が必要です。

変換器モデルはOPAL-RTが独自に開発し、FPGA上で駆動させることが出来るモデルを使用しました。

詳細はこちらをご参照ください。

→ ARTEMiS

通常HILSを使用する場合、積分きざみの中間の時点でのパルス(固定ステップと固定ステップの中間) の処理が誤差の要因となります。

OAPL-RTは独自に開発したRT-Eventsという機能により、積分きざみの中間の時点でのパルスを20nsecという高精度の分解能で捉え、演算をすることが可能です。

リアルタイムシミュレーションの積分時間きざみは20μsで、SimPowerSystemで行なった結果と重ねています。

シミュレーションは充電モードでの整流動作ですが、両者は非常によく一致しています。

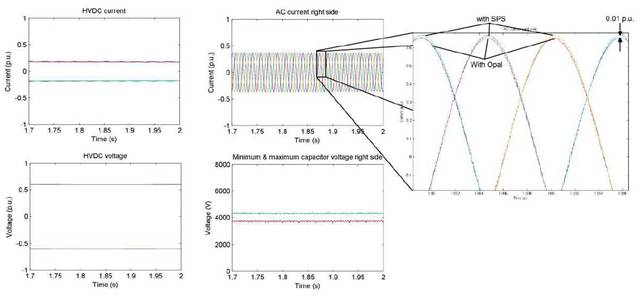

Fig.4 定常状態波形(出力0.6pu) ―Simscape Electrical™(旧SimPowerSystems™)とOpal-RTモデルの結果

Fig.4は定常状態のシミュレーションです。

誤差は0.025pu以下です。

Simscape Electrical™(旧SimPowerSystems™)でのオフラインシミュレーション(1μsec)の結果とOPAL-RTのHILSを使った結果は、AC側の電流値のピークの誤差が0.01pu程度になっています。

この結果はシミュレーションとしては非常に良い結果と言えます。

Fig.5 系統故障時のシミュレーション ― Simscape Electrical™(旧SimPowerSystems™)とOpal-RTモデルの結果

Fig.5は系統故障時のシミュレーション結果です。

この場合もよく一致しています。

赤色のグラフがSimscape Electrical™(旧SimPowerSystems™)(1μsec)でのオフラインシミュレーションの結果、青色のグラフがOPAL-RTのHILSを使った結果です。

それぞれHVDC電流とHVDC電圧のシミュレーション結果を示しています。

HVDC電流ではピーク値で0.01puの、HVDC電圧ではピーク値で0.02puの誤差が観測されています。

これもシミュレーションとしては非常に良い結果です。

Fig.6 IOで接続された2台のHILSシステム

Fig.6は2台のHILSシステム (Target)のIO接続の状態です。

MMCのリアルタイムシミュレーションでは各々180個ずつのデジタル/アナログ信号を、20μsecの制御周期で入出力する必要があります。

そのためIO関係はすべてFPGAによってコントロールされています。

FPGAでコントロールされた場合、アナログ入出力のハードによる信号遅延は約1.2μsec程度です。

この遅れは実コントローラを使用した場合でも多少の遅延は起きる為、実用上は問題になることは普通ありません。

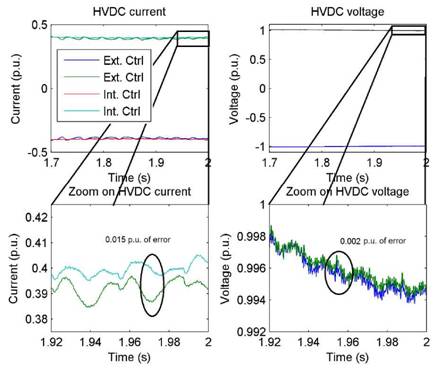

Fig. 7制御装置を外部に置いた場合のHVDC電流、電圧とその誤差

Fig.7は、制御系を外部においた場合のHVDC電流と電圧の波形です。

リアルタイムシミュレータHILSを使った一般的な開発手順は、先ず最初にコントローラアルゴリズムをバーチャルモデルとして、一台のHILS上に 構成します。

最初にプラントモデルがあるTarget1に全てのモデルを構築し、リアルタイムでデジタルシミュレーションを行います。

この段階で制御アルゴリズムの論理的な検証が行われます。

それがOKとなった後、次にコントローラの部分をTarget2に構築し、実際のIO(アナログ デジタル)を使用して実際のコントローラを使った場合の整合性を確認します。

Int Ctrlが制御モデルをTarget1に置いた場合、Ext CtrlがTarget1とTarget2にモデルを分けた場合の信号です。

制御系を外部に置いた場合は信号伝送の遅れがあり、それが電流の差として現れている状態が観測されます。

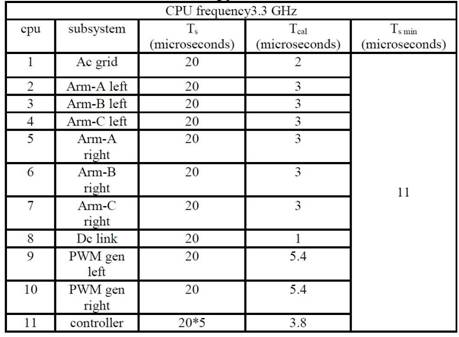

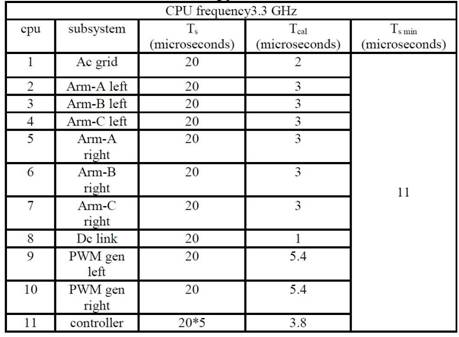

表1 リアルタイムシミュレーションの時間特性

表1は、11個のCPUコアを使った場合の演算時間です。

CPUのクロック周波数を3.3GHzを使った場合の全体の制御ステップは20μsになります。

モデル上の各サブシステムの演算時間を計測した結果を表にしております。

それぞれのCPUコアの演算時間は1~5.4μsです。

Ts_minの11μsはこのケースで実現できる最小の制御ステップになります。

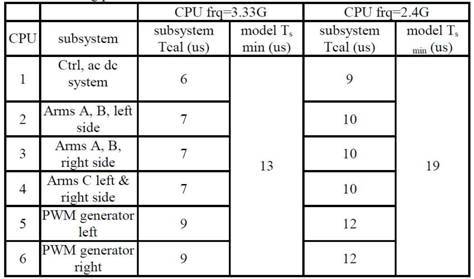

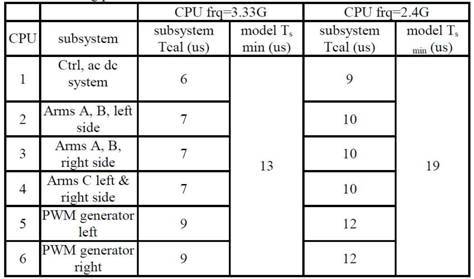

表2 6CPUの時間特性

表2は、6個のCPUコアを使った場合で、CPUのクロック周波数を3.3GHzと2.4GHzを使用した場合の比較です。

CPUコアの数が減ると(11個から6個)リアルタイム計算が可能な最小制御ステップも13μsと長くなります。

また、クロック周波数が遅くなると最小制御ステップも長くなります。

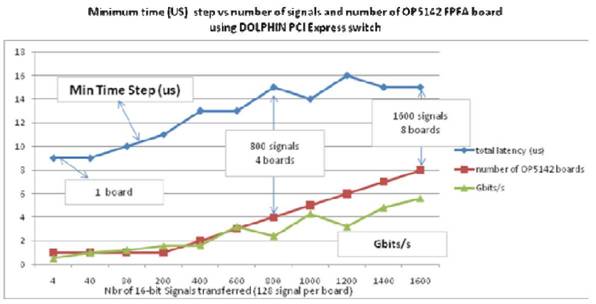

Fig. 8 制御ステップ時間 と 信号数の関係

今回のテストではデジタルI/OとアナログI/Oをそれぞれ180個ずつ使用しました。

実際にはもっと多くのI/Oが使用され、その処理時間だけで非常に多くの処理時間が必要になります。

Fig.8は信号数を1600まで増加させた場合の特性を検討したものです。

信号数の増加に合わせてPCIバス直結の専用I/Oボードの数も増えています。

(1600信号の時は8ボード必要です)

I/Oの数が1600個になった場合でも、最小制御ステップは16μsで収まることが予測されます。

これらのテストが行われたのは2011年の段階ですので、CPUのクロックはその時点での最新のものを使用していますが、現在は当時より速くなっております。

さらに最近はIGBT等アームの全ての挙動をFPGAにおくことが主流になっていますので、全体の制御ステップはμsecからnsecオーダーまで高速化されております。

詳細は下記のページをご参照ください。

→ OP7000

CPUベースのeMEGAsimリアルタイムシミュレータは以下の特徴があります。

- IOの数が360(デジタル・アナログそれぞれ180個)あるMMCのリアルタイムシミュレーションは20μsの制御ステップ時間で実行可能。

- 20μs制御ステップを実現するMMCモデルの精度は充分実用に耐える。

-

リアルタイムシミュレータの結果とオフライン計算の結果に誤差が出ているが、主な原因は IO信号の伝送遅れによるものである。

ただ 実機でも点弧信号の伝送遅れはあるので、オフラインシミュレーションでも伝送遅れを考慮する必要がある。 - HILSを使った場合、実時間の200倍の速度でシミュレーションすることも可能である。

-

制御ステップ時間をもっと速くしようとすると、もっと多くのFPGAが必要になる。

現在は全体を250nsecの制御周期で実行可能なFPGAシミュレータが主流になりつつある。

OPAL-RTのリアルタイムシミュレータはMMCのスイッチング現象を含めた複雑なプラントの動きを正確に模擬し コントローラの制御アルゴリズムの検証に非常に有効な手段。