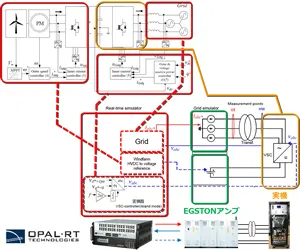

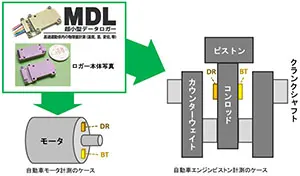

OPAL-RT社のHILシステムの特徴

MATLAB® Simulink®ベース・多チャンネルI/O対応HILシステム

CPU/FPGAハイブリッドモデル対応HILシステム

HIL/HILS(ハードウェア・イン・ザ・ループ)モデル構造

XILINX社製FPGAの実行速度を活かした高速なパワエレ回路・モータモデルと、Intel社製XEON CPUのパフォーマンスを活かした大規模な数式・系統モデルを同時に実行し、相互に通信を行い、連携する事が出来ます。

OPAL-RTのFPGAテクノロジー"eHs"は、専用回路エディタ"SchematicEditor"で簡単にパワエレ回路を作製する事が出来ます。

FPGAモデルにありがちな、数時間~数日にも及ぶ長大なコンパイルは無く、数舜~数分程度でビルドが完了します。

FPGA側日のパワエレ回路にSimScapeElectricalを使用した場合

eHSには、専用回路エディタの代わりに、MATLAB® Simulink®のSimScapeElectricalを使用する事も出来ます。

MATLAB® Simulink®ベースHILシステム

構成概要

HILシステムのCPUは4コア、8コア、16コアから選択可能で(※OP5707XGの場合)、MATLAB® Simulink®で作製した大きな数式モデルも、複数コアに分割して同時実行する事が可能です。

"ARTAMiS"に、"ARTEMiS SSN"を追加する事で、SimScapeElectricalを使用したも複数コアに対応する事が出来る様になり、更に長距離送電にも対応可能となります。

"Orchestra"ソルバーを追加する事で、協調シミュレーション(CO-SIMULATION)に対応させる事も可能です。(例:8枚全てをデジタル入力に割り当てた場合、32ch×8 = 256ch)

OPAL-RTのHIL筐体は、拡張ボックスを追加する事で、更に多くのI/Oチャンネル数に拡張する事も可能です。

多チャンネル対応

自由にレイアウトしたI/Oモジュールの各入出力チャンネルは、筐体背面のD-SUBコネクタ上の各ピンに割り当てられます。これらの各チャンネルは、RT-LABのSimulinkモデルおよび、eHS SchematicEditorの電源、電圧・電流計、モータのセンサーに、自由に割り当てて使用する事が出来ます。

HIL接続と同時にオシロで波形を観測可能

通常のHIL筐体は、一旦、実機コントローラとHIL接続してしまうと、その間で交わされる電気信号をオシロで観測する事が出来ません。もしくは、専用の回路の作製が必要となります。OPAL-RTのHIL筐体は、オシロ接続用ポートを備えており、任意の4チャンネル(×4)をオシロに接続して波形観測する事が可能です。

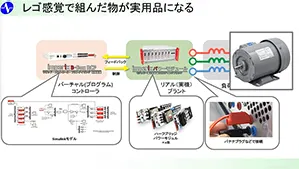

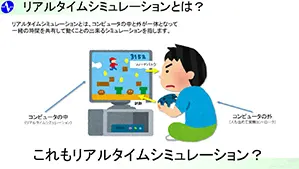

リアルタイムMIL

これを用いる事で、HILシステムのモデルでPWMを生成する事が出来る様になり、RCPへの対応も可能となります。

RCP用のコントローラモデルと、HIL用のプラントモデルを利用する事で、1筐体に一人二役を担わせる"リアルタイムMIL"(ループバックテスト)が可能となります。

愛知県名古屋市千種区池下1-11-21

TEL:052-764-3311 FAX:052-764-3632

TEL:052-764-3311 FAX:052-764-3632

1751 Rue Richardson office 1060, Montréal, Québec H3K 1G5, Canada

TEL:+1-514-935-2323

TEL:+1-514-935-2323

* 記載の会社名および製品名は、各社の登録商標および商標です。